引言

稅控收款機是指具有特定稅控功能的電子收款機,它是集軟硬件為一體的嵌入式系統,硬件設計考慮高性價比和高可靠性,軟件設計考慮系統的穩定性和可靠性。根據這一原則,本文介紹了一種基于ARM控制器LPC2214的稅控收款機的設計方案。

稅控收款機硬件系統的設計與實現

稅控收款機的硬件組成框圖如圖1所示,其硬件系統由中央處理模塊、顯示模塊、打印模塊、電源模塊、時鐘模塊、IC卡接口、外部通訊接口(包括RS232串行接口、網絡接口、USB接口等)、蜂鳴器,以及輸入鍵盤、電子鎖、條碼掃描儀和手寫板等幾部分組成。

圖1 稅控收款機硬件框圖

中央處理模塊

中央處理模塊采用飛利浦公司基于32位ARM7TDMI-S內核的低功耗ARM處理器LPC2214。該處理器是飛利浦公司為嵌入式應用提供的高性價比微控制器解決方案,通過在ARM7TDMI-S內容基礎上擴展一系列的通用外圍器件,使系統費用降至最低,增強了系統對外部設備的支持能力。由于LPC2114集成了豐富的片上資源,所以系統本身的擴展大大減少,這不但減小了產品的體積,而且便于維護。

顯示模塊

作為人機交互的顯示模塊包括一個LCD主顯示屏和一個9位的VFD用戶顯示屏,其中LCD采用內置KS0107/KS0108控制器的圖形點陣式液晶,顯示分辨率為192×64,可顯示16×5個11×12點陣的漢字;VFD通過具有SPI接口的芯片HT16512進行驅動。

打印模塊

系統選用EPSON公司的MU110II打印機頭,供電電壓為DC24V。電機驅動采用MTD2003F,針驅動采用MTA001M,由LPC2214的通用I/O口進行控制。

電源管理模塊

系統采用開關電源為LPC2214提供5V電源。由于稅控收款機對掉電保護有嚴格要求,所以在電源管理模塊中設計了掉電保護電路,可以在掉電時維持系統正常工作一定時間。掉電時該電路會發送給處理器一個中斷,使系統進入掉電中斷處理程序,進行相應的掉電保護工作。

時鐘模塊

時鐘模塊采用I2C總線時鐘芯片P8563AP,在后備電池的支持下,能保證系統掉電后片內時鐘繼續運行。

稅控存儲器

稅控收款機需要記錄大量的數據信息,本系統采用了ATMEL公司具有SPI接口的Flash存儲器AT45DB321,由于LPC2214微控制器具有SPI的接口,所以能夠方便地同它相連接。設計上采用可插拔式模塊,將數據存儲模塊與系統主板分離。此設計的特點是當系統出錯時,能夠將重要數據及時轉移,降低了數據發生錯誤的幾率,提高了數據的完整性和可靠性。在稅控卡的配合下,可以將相關的數據信息轉移到另一正常工作的機器中繼續進行工作,保證數據存儲的時效性。另外,也可以在維護和檢修時采用替換法,這體現出很強的實用性和可操作性。

IC卡接口

通常的設計中會使用專用IC卡讀寫芯片為系統提供ISO7816的接口,如CTS56I01、WatchCore、TDA8020等。本系統沒有進行硬件擴展,充分利用LPC2214的性能特性,實現了符合ISO7816標準的IC卡接口功能。

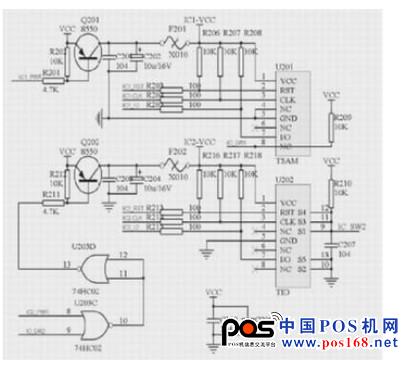

智能卡芯片的接口信號包括:電源電壓(VCC)、地(GND)、復位(RST)、時鐘(CLK)、編程電壓(VPP)、輸入輸出(I/O)。如圖2所示,I/O、RST由LPC2214微控制器的通用I/O口(GPIO)來控制,通過軟件模擬數據讀寫操作時序,實現數據的交換,其中I/O上信號的傳輸是雙向的,所以要利用軟件根據時序不斷轉換輸入輸出的狀態。此方法具有成本低、方便靈活等特點。

電源管理模塊

系統采用開關電源為LPC2214提供5V電源。由于稅控收款機對掉電保護有嚴格要求,所以在電源管理模塊中設計了掉電保護電路,可以在掉電時維持系統正常工作一定時間。掉電時該電路會發送給處理器一個中斷,使系統進入掉電中斷處理程序,進行相應的掉電保護工作。

時鐘模塊

時鐘模塊采用I2C總線時鐘芯片P8563AP,在后備電池的支持下,能保證系統掉電后片內時鐘繼續運行。

稅控存儲器

稅控收款機需要記錄大量的數據信息,本系統采用了ATMEL公司具有SPI接口的Flash存儲器AT45DB321,由于LPC2214微控制器具有SPI的接口,所以能夠方便地同它相連接。設計上采用可插拔式模塊,將數據存儲模塊與系統主板分離。此設計的特點是當系統出錯時,能夠將重要數據及時轉移,降低了數據發生錯誤的幾率,提高了數據的完整性和可靠性。在稅控卡的配合下,可以將相關的數據信息轉移到另一正常工作的機器中繼續進行工作,保證數據存儲的時效性。另外,也可以在維護和檢修時采用替換法,這體現出很強的實用性和可操作性。

IC卡接口

通常的設計中會使用專用IC卡讀寫芯片為系統提供ISO7816的接口,如CTS56I01、WatchCore、TDA8020等。本系統沒有進行硬件擴展,充分利用LPC2214的性能特性,實現了符合ISO7816標準的IC卡接口功能。

智能卡芯片的接口信號包括:電源電壓(VCC)、地(GND)、復位(RST)、時鐘(CLK)、編程電壓(VPP)、輸入輸出(I/O)。如圖2所示,I/O、RST由LPC2214微控制器的通用I/O口(GPIO)來控制,通過軟件模擬數據讀寫操作時序,實現數據的交換,其中I/O上信號的傳輸是雙向的,所以要利用軟件根據時序不斷轉換輸入輸出的狀態。此方法具有成本低、方便靈活等特點。

圖2 稅控收款機IC卡接口

業務處理層設計

業務處理層是稅控收款機軟件架構中的最上層,與具體的硬件平臺無關,作為一個應用軟件可方便地移植到不同的硬件平臺上。該層用于實現商務和稅控兩大主要功能,由4個模塊組成。

主程序(主控模塊)進行系統自檢、軟硬件的初始化、調度運行業務處理層的其它模塊以及處理掉電數據恢復、數據整理,并控制整個軟件的流程;稅控功能模塊實現GB18240-2003國家標準中的稅控功能,負責機器初始化和注冊、發票的購買分發、開發票(包括退票、廢票處理)、稅控數據申報、監控數據回送、稅務核查等;商務功能模塊由銷售子模塊、統計分析(報表)子模塊、設置管理子模塊以及其它一些功能子模塊組成;通訊模塊負責與運行在上位機(PC)上的稅控收款機管理系統進行數據通信。

接口層設計

接口層作為一個抽象層僅提供應用程序接口,不對具體硬件操作,也不處理具體業務,是針對復雜設備設計的管理程序,主要包括IC卡管理、存儲器管理、USB通訊管理等。以下詳細介紹存儲器管理中的發票存儲管理模塊。

稅控收款機要求能夠可靠存儲大量發票數據,因此發票存儲管理模塊是本系統的一個關鍵模塊。為了節約存儲空間,本系統中發票存儲系統采用了變長滾動存儲方法。

變長即指發票長度因各發票頭部和其所含明細的不同,占用的存儲空間大小也不同。本系統中發票頭部分別可能占用32、64、96字節,發票最大明細數為8,每筆明細占用32字節。這樣,每張發票所占存儲空間為1個~11個32字節。發票在存儲器中的存儲位置也是以32字節為單位對齊的,兩張發票之間位置首尾相連,沒有冗余空間。

滾動存儲即指在存儲空間固定的情況下,循環利用這部分存儲空間,當所存儲的發票占用到了足夠大的空間時,新的發票可能會覆蓋掉最早存儲的發票位置。

由于發票變長存儲,所占空間大小不一,為了達到隨機訪問的目的,需要建立一張位置索引表,表中的每項指明發票的實際存儲位置,比如,位置索引表中的第n項就是第n張發票在存儲器中的位置。同時,為了加快通過發票號查找發票詳細信息的查找速度,要最大可能地減少對存儲器的訪問次數,這是提高查找速度的關鍵。本系統采用Hash索引表來快速定位所要查找的發票,為了解決該算法的Hash值計算沖突,另外建立了一張Hash鏈接表,此表的長度和位置索引表相同,表中每個值代表Hash值沖突的下一張發票的位置。

設備驅動層設計

設備驅動層包括直接操作外設的驅動,如IC卡、Flash、LCD、VFD、打印機、USB、鍵盤、時鐘等外設的驅動;另外還包括LPC2214內部配置驅動,如內部寄存器配置、UART配置、GPIO設置、RTC讀寫、TIMER設置等。其中ISO7816標準IC卡驅動是一個關鍵部分,它包含插卡檢測、卡上下電、卡復位和卡命令等功能。

IC卡與LPC2214微控制器的數據傳輸方式為異步半雙工字符傳輸模式,本系統使用軟件實現該功能。利用LPC2214的GPIO來軟件模擬IC卡的讀寫操作時序,進行數據交換:接收數據時將LPC2214的GPIO設置為輸入模式,使用中斷程序對I/O數據線進行采樣;發送數據時將LPC2214的GPIO設置為輸出模式,在中斷程序中直接輸出需要發送的數據位。

異常情況處理

當異常情況(如斷電、拔卡等)發生時,稅控收款機應保證數據不丟失、無差錯。本系統從兩方面保證了數據的可靠性。一方面,在初始化、分發發票、錄入發票、開票、報稅及完稅等關鍵步驟前先檢測電源是否正常,如已經發生掉電,系統停止工作;否則置標志,開始正常的步驟操作,步驟完成后,清除標志。如果步驟未完成前發生斷電或IC卡意外拔出等事件,則在下一次上電或重新操作該步驟時系統會檢測到標志,軟件將自動調用恢復機制,完成剩余操作,恢復丟失的數據。

本網站部分內容來源于網站會員、合作媒體、企業機構、網友提供和互聯網的公開資料等,僅供參考。本網站對站內所有資訊的內容、觀點保持中立,不對內容的準確性、可靠性或完整性提供任何明示或暗示的保證。如果有侵權等問題,請及時聯系我們,我們將在收到通知后第一時間妥善處理該部分內容。